- 您现在的位置:买卖IC网 > Sheet目录478 > MMA6556KW (Freescale Semiconductor)IC ACCELEROMETER X AXIS 16QFN

�� �

�

3.1.11�

�Device� Status� Register� (DEVSTAT)�

�The� device� status� register� is� a� read-only� register.� A� read� of� this� register� clears� the� status� flags� affected� by� transient� conditions.�

�Reference� Section� 4.5� for� details� on� the� response� for� each� status� condition.�

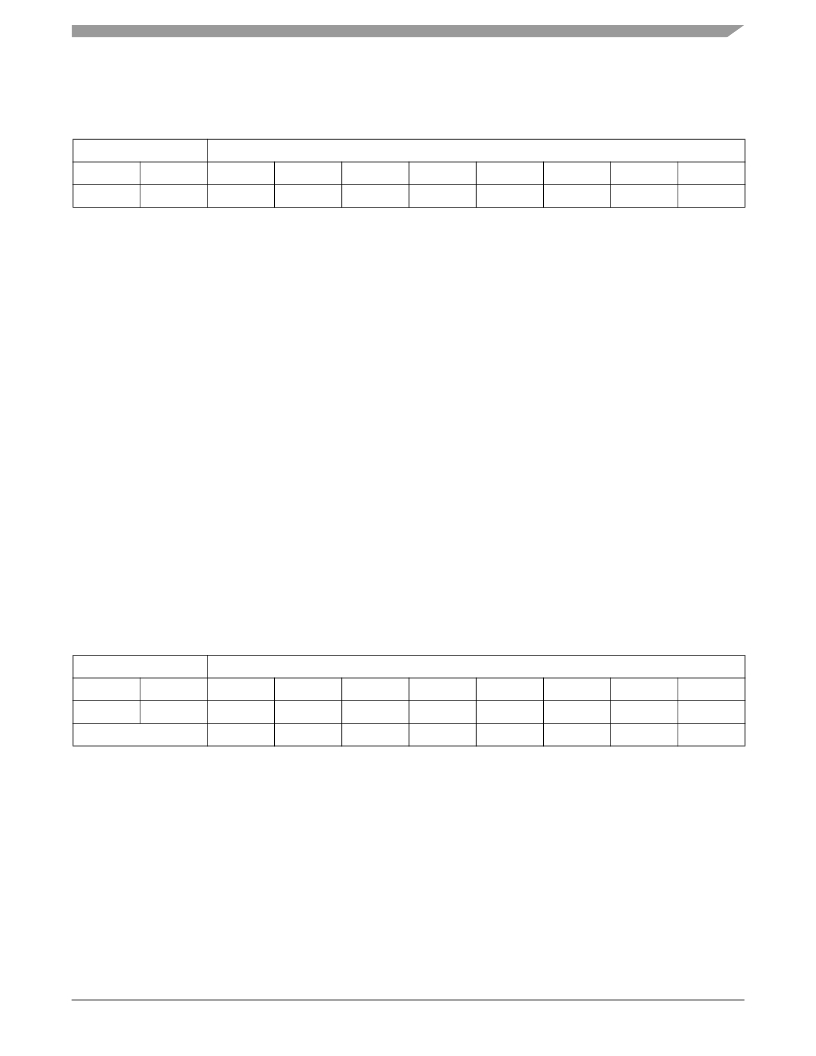

�Table� 19.� Device� Status� Register�

�Location�

�Bit�

�Address�

�$14�

�Register�

�DEVSTAT�

�7�

�UNUSED�

�6�

�IDE�

�5�

�UNUSED�

�4�

�DEVINIT�

�3�

�MISOERR�

�2�

�0�

�1�

�OFFSET�

�0�

�DEVRES�

�3.1.11.1� Unused� Bits� (UNUSED)�

�The� unused� bits� have� no� impact� on� operation� or� performance.� When� read� these� bits� may� be� ‘1’� or� ‘0’.�

�3.1.11.2� Internal� Data� Error� Flag� (IDE)�

�The� internal� data� error� flag� is� set� if� a� customer� or� OTP� register� data� CRC� fault� or� other� internal� fault� is� detected� as� defined� in�

�Section� 4.5.5� .� The� internal� data� error� flag� is� cleared� by� a� read� of� the� DEVSTAT� register.� If� the� error� is� associated� with� a� CRC� fault�

�in� the� writable� register� array,� the� fault� will� be� re-asserted� and� will� require� a� device� reset� to� clear.� If� the� error� is� associated� with� the�

�data� stored� in� the� fuse� array,� the� fault� will� be� re-asserted� even� after� a� device� reset.�

�3.1.11.3� Device� Initialization� Flag� (DEVINIT)�

�The� device� initialization� flag� is� set� during� the� interval� between� negation� of� internal� reset� and� completion� of� internal� device� ini-�

�tialization.� DEVINIT� is� cleared� automatically.� The� device� initialization� flag� is� not� affected� by� a� read� of� the� DEVSTAT� register.�

�3.1.11.4� SPI� MISO� Data� Mismatch� Error� Flag� (MISOERR)�

�The� MISO� data� mismatch� flag� is� set� when� a� MISO� Data� mismatch� fault� occurs� as� specified� in� Section� 4.5.2� .� The� MISOERR�

�flag� is� cleared� by� a� read� of� the� DEVSTAT� register.�

�3.1.11.5� Offset� Monitor� Error� Flags� (OFFSET)�

�The� offset� monitor� error� flag� is� set� if� the� acceleration� signal� reaches� the� specified� offset� limit.� The� offset� monitor� error� flags� are�

�cleared� by� a� read� of� the� DEVSTAT� register.�

�3.1.11.6� Device� Reset� Flag� (DEVRES)�

�The� device� reset� flag� is� set� during� device� initialization� following� a� device� reset.� The� device� reset� flag� is� cleared� by� a� read� of�

�the� DEVSTAT� register.�

�3.1.12�

�Count� Register� (COUNT)�

�The� count� register� is� a� read-only� register� which� provides� the� current� value� of� a� free-running� 8-bit� counter� derived� from� the� pri-�

�mary� oscillator.� A� 10-bit� pre-scaler� divides� the� primary� oscillator� frequency� by� 1024.� Thus,� the� value� in� the� register� increases� by�

�one� count� every� 128� μ� s� and� the� counter� rolls� over� every� 32.768� ms.�

�Table� 20.� Count� Register�

�Location�

�Bit�

�Address�

�$15�

�Register�

�COUNT�

�7�

�COUNT[7]�

�6�

�COUNT[6]�

�5�

�COUNT[5]�

�4�

�COUNT[4]�

�3�

�COUNT[3]�

�2�

�COUNT[2]�

�1�

�COUNT[1]�

�0�

�COUNT[0]�

�Reset� Value�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�MMA655x�

�Sensor�

�Freescale� Semiconductor,� Inc.�

�19�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MMA6826AKW

IC ACCELEROMETER XY AXIS 16QFN

MMA6854KW

IC ACCELEROMETER X AXIS 16QFN

MMA7331LR2

ACCELEROMETER 4G XYZ ENH 14-LGA

MMA8451QT

IC ACCELEROMETER 3AXIS 16QFN

MMA8452QR1

IC ACCELER 2G/4G/8G 3AXIS 16QFN

MMA8453QR1

IC ACCELER 2G/4G/8G 3AXIS 16QFN

MMBF0201NLT1

MOSFET N-CH 20V 300MA SOT-23

MMBF170-7

MOSFET N-CH 60V 500MA SOT23-3

相关代理商/技术参数

MMA6556KWR2

功能描述:加速计 - 板上安装 X-AXIS 120G RoHS:否 制造商:Murata 传感轴:Double 加速:12 g 灵敏度: 封装 / 箱体: 输出类型:Analog 数字输出 - 位数:11 bit 电源电压-最大:5.25 V 电源电压-最小:4.75 V 电源电流:4 mA 最大工作温度:+ 125 C 最小工作温度:- 40 C

MMA65XX

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Dual-Axis SPI Inertial Sensor

MMA6700AEGR2

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:High Accuracy Low g Inertial Sensor MEMS Sensing, State Machine ASIC

MMA6700EG

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:High Accuracy Low g Inertial Sensor MEMS Sensing, State Machine ASIC

MMA6700EGR2

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:High Accuracy Low g Inertial Sensor MEMS Sensing, State Machine ASIC

MMA6701AEGR2

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:High Accuracy Low g Inertial Sensor MEMS Sensing, State Machine ASIC

MMA6701EG

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:High Accuracy Low g Inertial Sensor MEMS Sensing, State Machine ASIC

MMA6701EGR2

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:High Accuracy Low g Inertial Sensor MEMS Sensing, State Machine ASIC